Filter Design HDL Coder genera codice VHDL® e Verilog® sintetizzabile e portabile per l’implementazione di filtri a virgola fissa, progettati con MATLAB, su FPGA o ASIC. Consente di creare automaticamente test bench VHDL e Verilog per la simulazione, il testing e la verifica del codice generato.

Inizia ora:

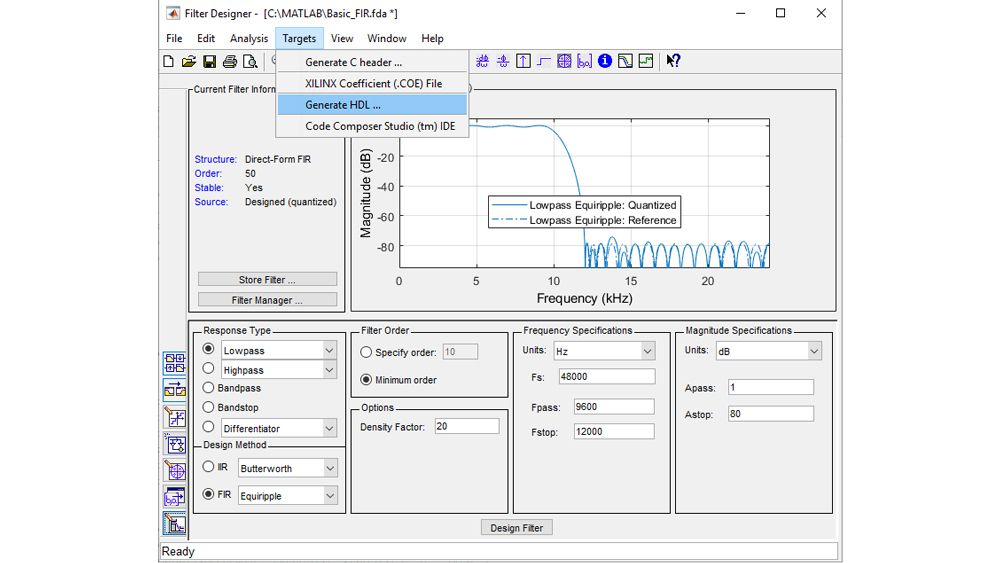

Filter Design HDL Coder è integrato con DSP System Toolbox per fornire un ambiente di progettazione e implementazione unificato. Puoi progettare filtri e generare codice VHDL e Verilog sia dalla riga di comando MATLAB che da DSP System Toolbox tramite l’applicazione Filter Design and Analysis o l’applicazione Filter Builder.

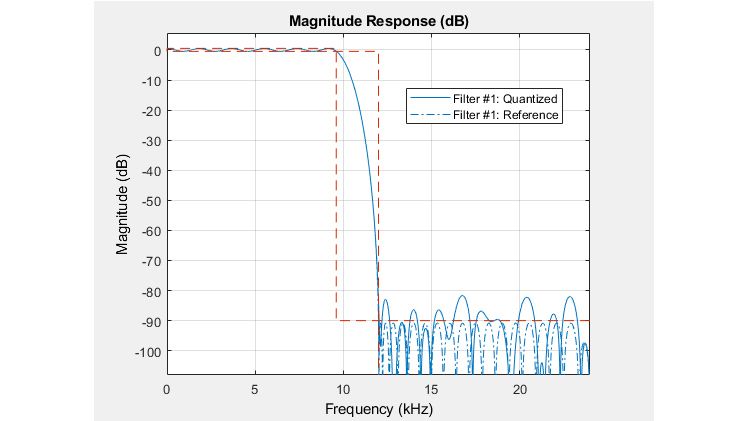

L’input di ingresso del progetto in Filter Design HDL Coder è un filtro quantizzato che puoi creare in uno dei seguenti due modi:

- Progettazione e quantizzazione del filtro con DSP System Toolbox

- Progettazione del filtro con Signal Processing Toolbox e quantizzazione con DSP System Toolbox

Filter Design HDL Coder supporta diverse strutture di filtri importanti, tra cui:

Risposta finita all’impulso (FIR) a tempo discreto, che include strutture simmetriche, antisimmetriche e trasposte

Risposta infinita all’impulso (IIR) SOS (second-order section), che include strutture a forma diretta I, II e trasposte.

Filtri multirate, che includono strutture di interpolatori e decimatori CIC (Cascaded Integrator-Comb), interpolatori e decimatori polifase FIR trasposti e FIR a forma diretta, interpolatori lineari e hold FIR e convertitori di frequenza di campionamento polifase FIR

Filtri di ritardo frazionario, che includono strutture Farrow

Filter Design HDL Coder può generare codice HDL a partire da filtri a tempo discreto e multirate in cascata. Ciascuna di queste strutture di filtri multirate e singlerate supporta realizzazioni a virgola fissa e mobile (doppia precisione). Inoltre, le strutture FIR supportano coefficienti a virgola fissa senza segno.

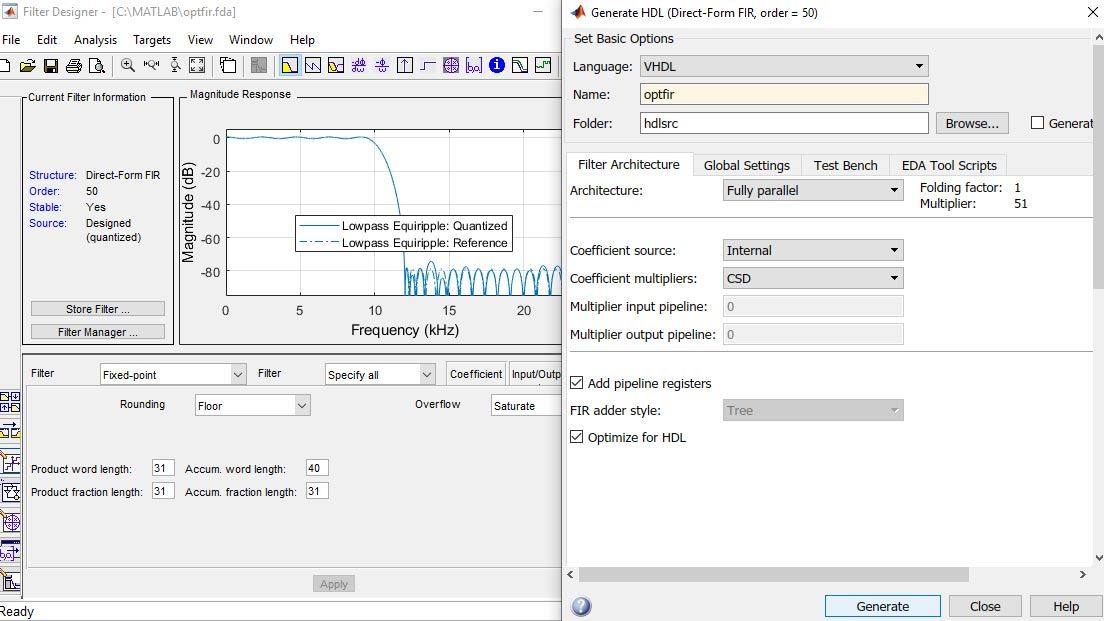

Puoi generare codice VHDL o Verilog per filtri a virgola fissa dall’app Filter Design and Analysis o dall’app Filter Builder. Durante la generazione di codice HDL da una delle due applicazioni, puoi impostare le opzioni di generazione HDL per specificare l’architettura di implementazione, selezionare i tipi di dati porta, inserire registri di pipeline e altro ancora. Altre opzioni ti consentono di generare e configurare un test bench per la progettazione del tuo filtro HDL.

Filter Design HDL Coder genera codice HDL di test bench e filtri per un filtro quantizzato in base all’impostazione di un’opzione o a coppie di valori di proprietà e di nomi di proprietà. Queste impostazioni ti consentono di:

- Rinominare gli elementi del linguaggio

- Specificare i parametri delle porte

- Utilizzare funzionalità di codifica HDL avanzate

Tutte le proprietà hanno impostazioni predefinite. Puoi personalizzare l’output di HDL regolando le impostazioni con l’app Filter Design and Analysis o con l’app Filter Builder. Le applicazioni ti consentono di impostare le proprietà associate a:

- Specifica del linguaggio HDL

- Specifiche di posizione e nome file

- Specifiche di reset

- Ottimizzazione del codice HDL

- Personalizzazione dei test bench

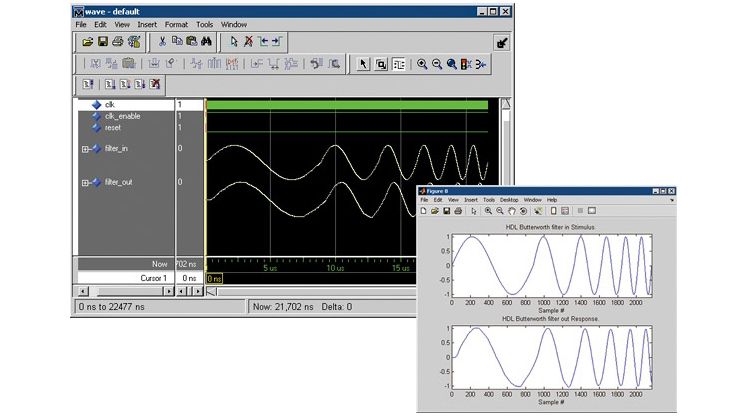

Puoi generare un test bench VHDL o Verilog per simulare e testare il codice HDL generato. Inoltre, con HDL Verifier, puoi generare un blocco di cosimulazione Simulink per collegare il tuo modello di filtro comportamentale e i test in esecuzione in Simulink all’HDL generato in esecuzione nei simulatori Cadence® Incisive® e Xcelium™ o nei simulatori Mentor® ModelSim® e Questa®. La cosimulazione semplifica la verifica della progettazione di filtri consentendo di mettere direttamente a confronto i risultati del codice HDL generato e quelli di un modello di filtro comportamentale in esecuzione in Simulink. Questa integrazione consente di applicare le funzionalità di visualizzazione e analisi avanzate di MATLAB e Simulink per testare, eseguire il debug e verificare l’implementazione HDL delle progettazioni di filtri.